UNION A Unified Inter/Intrachip Optical Network for Chip Multiprocessors

US$35.44

10000 in stock

SupportDescription

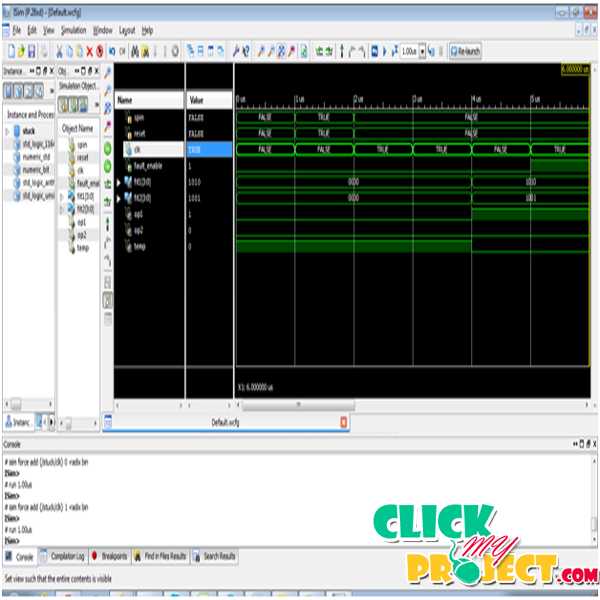

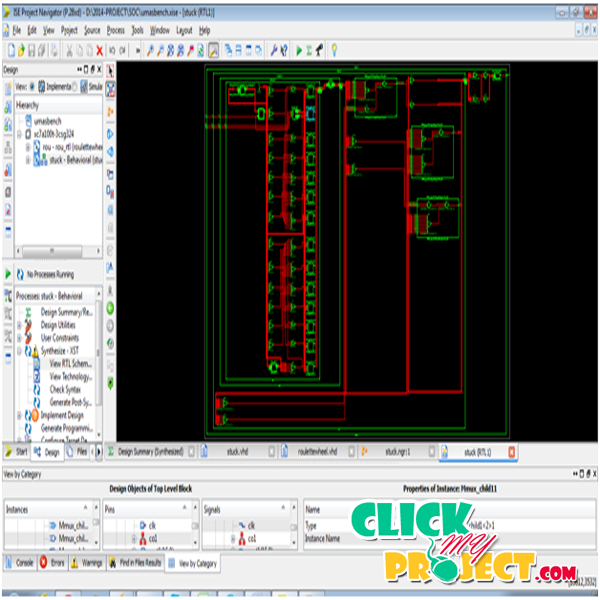

The network-on-chip (NoC) design problem requires the generation of a power and resource efficient interconnection architecture that can support the communication requirements for the SoC with the desired performance. The increasing number of intellectual property (IP) cores in multi-processor System-on-Chips (MPSoCs) makes NoC application mapping more challenging to find optimum core-to-topology mapping. The factorial increase in possible mappings One promising solution shown in recent studies is to add express channels to the network as shortcuts to bypass intermediate routers, thereby reducing packet latency. However, this approach also greatly changes the packet delay estimation and traffic behaviors of the network, both of which have not yet been exploited in existing mapping algorithms. In this paper, we present a new network-on-chip (NoC) that handles accurate localizations of the faulty parts of the NoC. The proposed NoC is based on new error detection mechanisms suitable for dynamic NoCs, where the number and position of processor elements or faulty blocks vary during runtime. Indeed, we propose online detection of data packet and adaptive routing algorithm errors. Both presented mechanisms are able to distinguish permanent and transient errors and localize accurately the position of the faulty blocks (data bus, input port, output port) in the NoC routers, while preserving the throughput, the network load, and the data packet latency. We provide localization capacity analysis of the presented mechanisms, NoC performance evaluations, and field-programmable gate array synthesis. In this project, present a new genetic algorithm to minimize test patterns for benchmark circuits. Genetic algorithms have been very effective for benchmark circuit test generation, especially when combined with deterministic algorithms. Time complexity is polynomial to generate the tests that detect all the stuck-at faults in these circuits. The proposed genetic algorithm uses Boolean functions in Sum-of-Products form. The fault-detection problem in benchmark circuits is formulated in a new framework. In the proposed work, evolutionary principles are employed in test minimization stage alone. Test minimization stage is cumbersome in deterministic and heuristic methods. Results show that test sets generated using the evolutionary approach are more compact than those generated by earlier approaches for many circuits. In addition, a survey on evolutionary techniques for optimizing the test set in digital circuits is performed. The surveyed methods are widely accepted by industries manufacturing digital circuits. A very brief introduction to entire flow of test minimization process is also presented.