Scan Test Bandwidth Management for Ultralarge Scale System on Chip Architectures

US$40.83

10000 in stock

SupportDescription

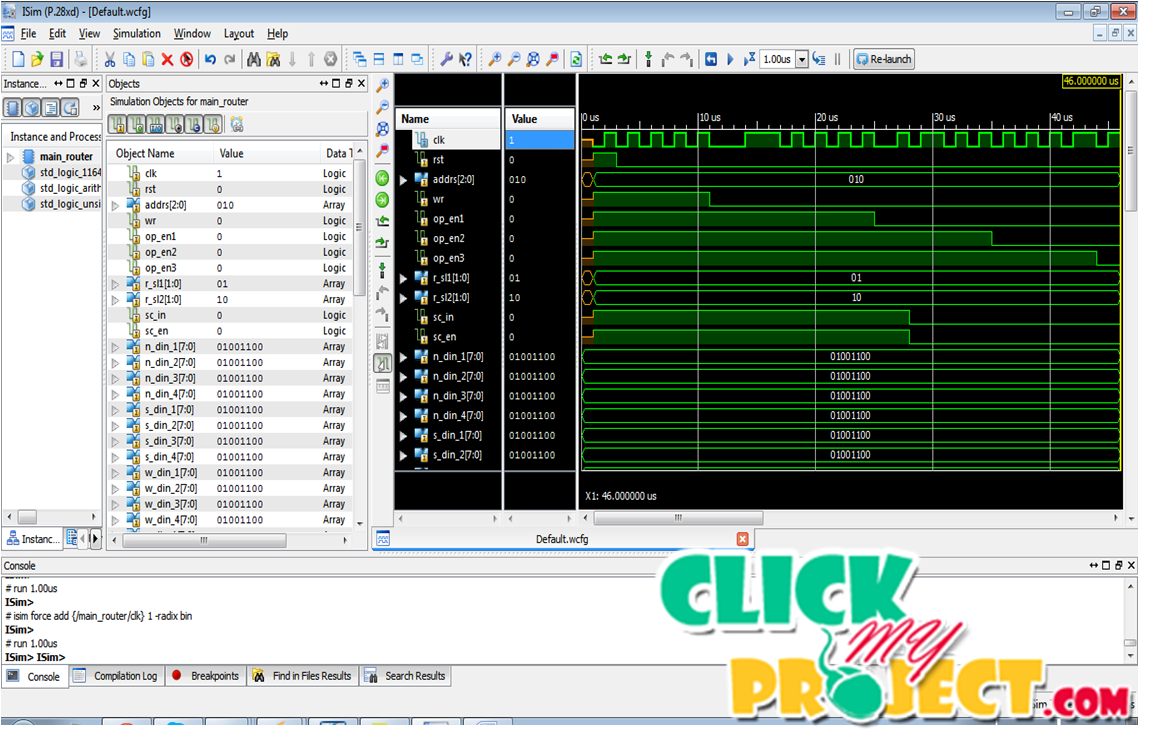

Network-on-Chip (NoC) architectures represent a promising design paradigm to cope with increasing communication requirements in digital systems. Network-on-chip (NoC) has emerged as a vital factor that determines the performance and power consumption of many core systems. VLSI technology is to modify NOC internal router arrangements, shortest path allocation process and neighbor router estimation control. In this architecture, our work is to design a 4*4 mesh topology based network on chip architecture using VCS technique. This work is to optimize the path allocation processing time and to increase NOC architecture performance level. Existing system is to design a mesh topology based network on chip architecture. This architecture is to implement the circuit switching and packet switching for path allocation process. Existing packet switching process is to identify the router availability for mesh topology based NOC architecture design and circuit switching process is used to identify the path availability for mesh topology NOC architecture. Existing system is to optimize the path allocation time and to effectively transmit the source to destination processing time level. Existing time is to increase the circuit complexity level and it consume more time for circuit analysis process. Existing system is to design a mesh topology based router architecture design and to optimize the path allocation process using hybrid scheme. This scheme is to consist of VCS, CS, PS technique for path allocation work. This work is to reduce the data transferring time between source and destination. Proposed method is to design a star topology based 4 * 4 NOC architecture using hop to hop router data transfer technique and this technique to reduce the path selection time. Proposed system is to implement the master and slave router condition for data transfer process and to optimize the path selection complexity level. This proposed architecture is to optimize the internal connectivity level and to reduce path allocation process level. This technique is to reduce data transfer time between source and destination. The proposed system is to consume less power and to reduce the circuit complexity also.