An Efficient Hybrid-Switched Network-on-Chip for Chip Multiprocessors

Our Price

₹4,500.00

10000 in stock

Support

Ready to Ship

Description

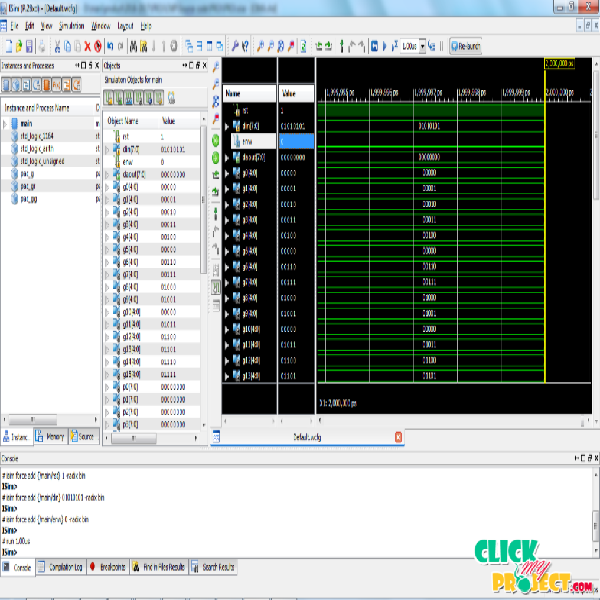

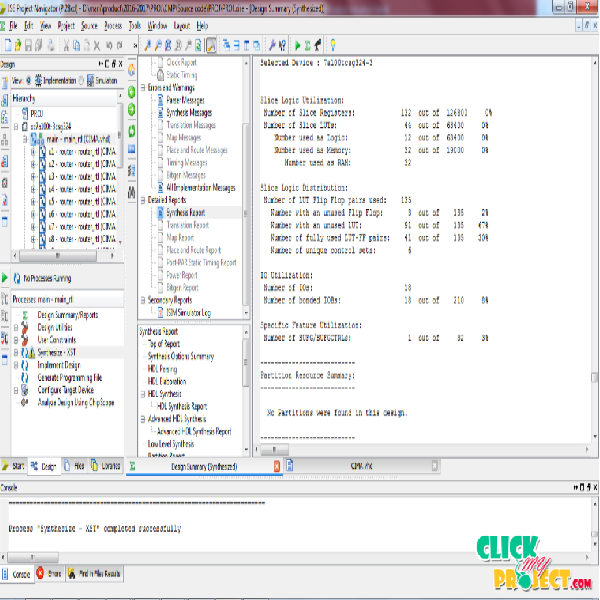

Chip multiprocessors (CMPs) require a low-latency interconnect fabric network-on-chip (NoC) to minimize processor stall time on instruction and data accesses that are serviced by the last-level cache (LLC). While packet-switched mesh interconnects sacrifice performance of many-core processors due to NoC-induced delays, existing circuit-switched interconnects do not offer lower network delays as they cannot hide the time it takes to set up a circuit. To address this problem, this work introduces CIMA—a hybrid circuit-switched and packet-switched mesh-based interconnection network that affords low LLC access delays at a small area cost.