Threshold Logic Computing Memristive CMOS Circuits for Fast Fourier Transform and Vedic Multiplication

₹3,500.00

10000 in stock

SupportDescription

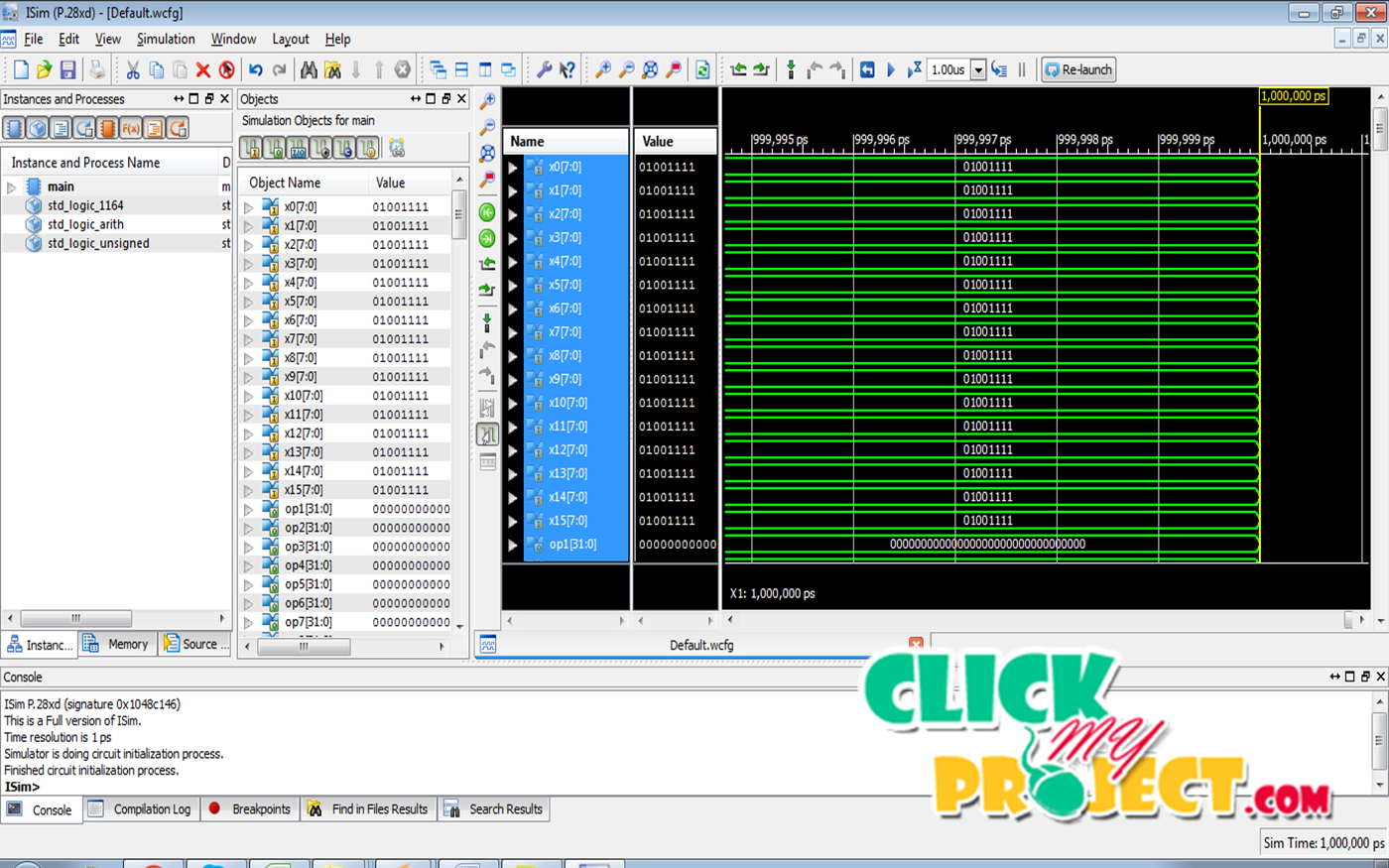

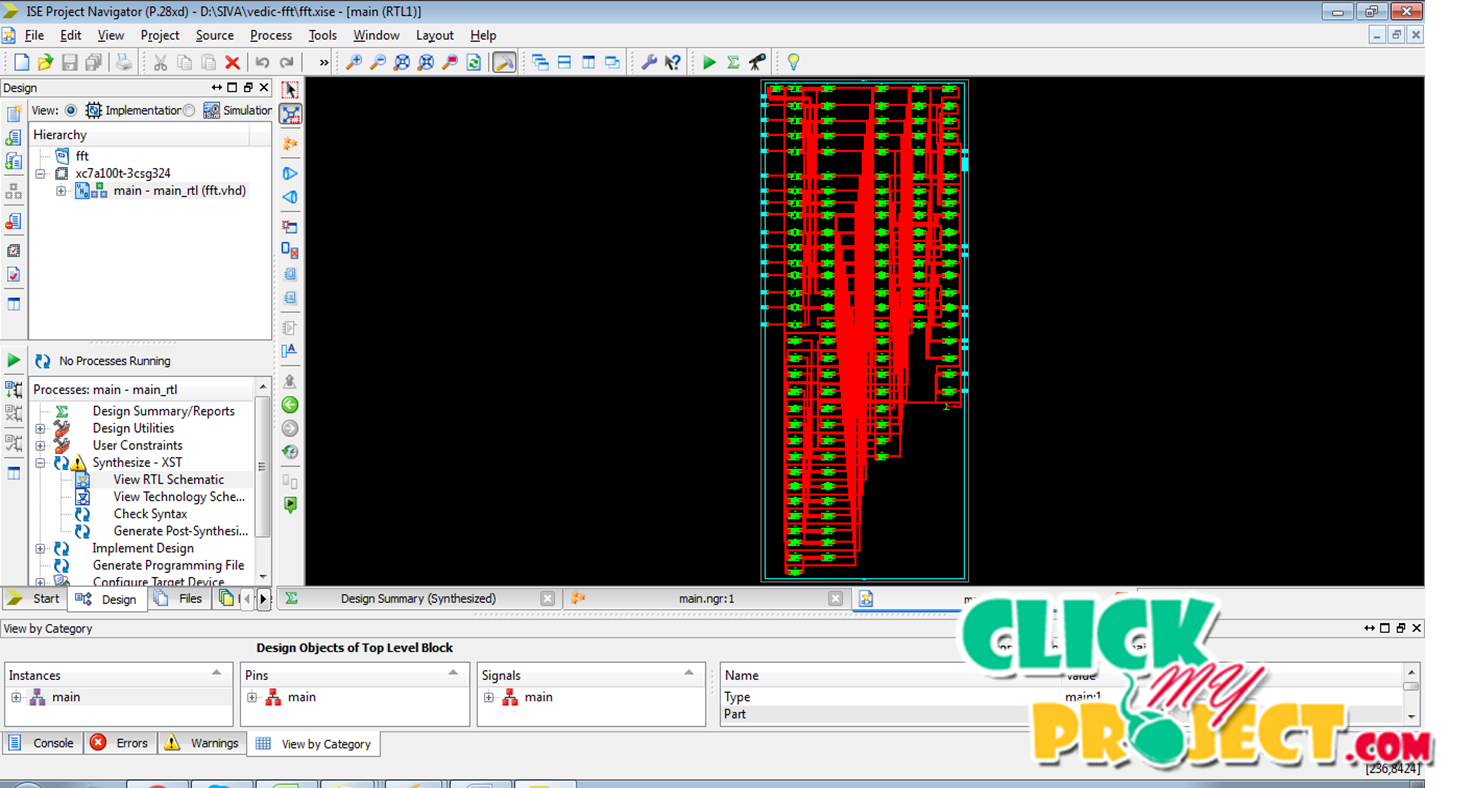

The progress in VLSI implementations of brain like logic gates is the scalability of the networks and its practical limitations in solving large variable Boolean logic problems.Thus the possibility is to apply the threshold logic gates in designing conventional computing based fast Fourier transform and the Vedic multiplication architecture.The real time pipelined FFT architectures have mainly been adopted to address the difficulties due to their attractive properties, such as small chip area, high throughput, and high speed operation. VLSI technology is used to modify the any type digital based hardware architecture and to reduce the hardware system power, speed and complexity level. The real time pipelined FFT architectures have mainly been adopted to address the difficulties due to their attractive properties, such as small chip area, high throughput, and high speed operation. This architecture is to reduce the register and bit reviser element. These architectures are is to perform the real and complex binary operation in 16-Point FFT adder, subtractor, vedic multiplier section.