Test Compaction by Sharing of Transparent-Scan Sequences Among Logic Blocks

Our Price

₹3,000.00

10000 in stock

Support

Ready to Ship

Description

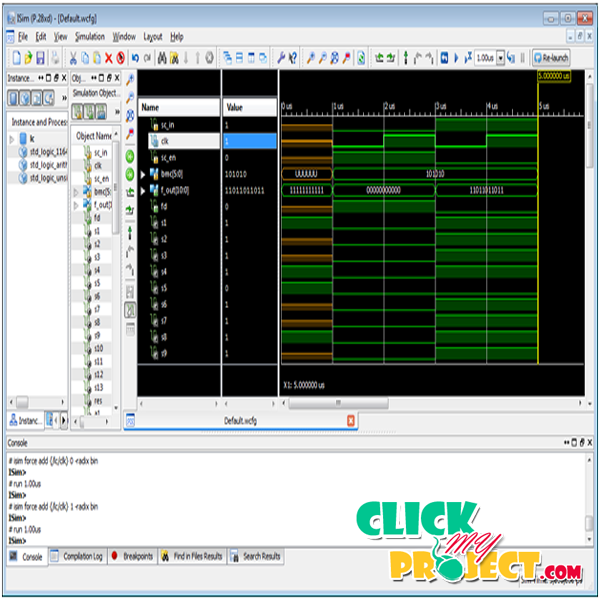

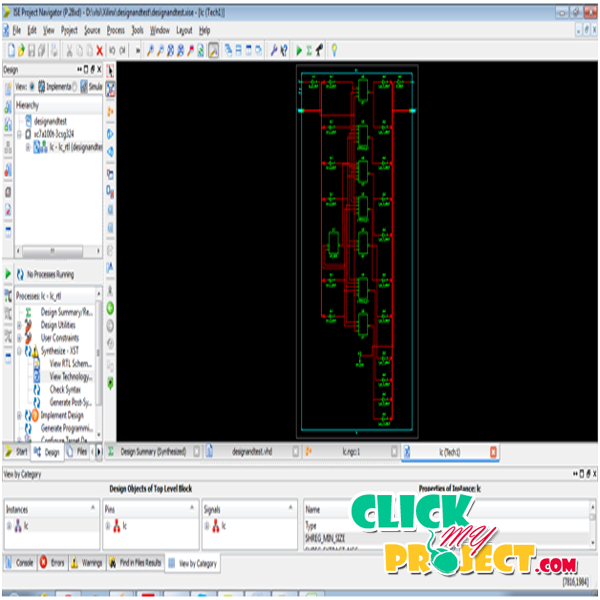

The testing architecture mainly used in all type of real world application architectures and thus the architecture to modified based on the enhancement purpose. The VLSI technology to optimize the any type of testing architecture. So the modification process used to the VLSI technology. The T-algorithm technique to optimize the testing LOC and LOS architecture. And the architecture used to the compare the test pattern results. In this architecture, T-algorithm used to optimize the testing architecture. This architecture compare the test pattern output for the required any type of combinational architecture. The optimization process mainly focused by gate optimization for secure architecture. The proposed system to use the T-algorithm, to optimize the testing clocking level for the required test patterns. This technique to replace the flip flop and the mux arrangement. To reduce the flip flops in LOS architecture. And to develop the accuracy for testing architecture. The proposed system consists of the secure testing architecture and includes the XOR-gate architecture. So the modification process applied by the LOC and over all LOS architecture. The proposed technique to check the scanning results for the testing process. The testing architecture mainly used to the error attack for the scanning process and the scanning process work with any type of testing architecture. The scanning process to be secure using the T-algorithm for the LOS architecture. And to develop the testing process for the fault identification process. The diagnosis technique to detect error for the scanning process in any type combinational architecture. The T-algorithm used to reduce the circuit complexity for the testing architecture and the testing architecture used to reduce the delay level. And the future process, this technique used to reduce the gate level for the sticky comparator architecture and to modify the clocking function for the testing process. This technique to develop the accuracy level for the testing process compare to the present methodology.