simplifying Clock Gating Logic by Matching Factored Forms

Our Price

₹3,000.00

10000 in stock

Support

Ready to Ship

Description

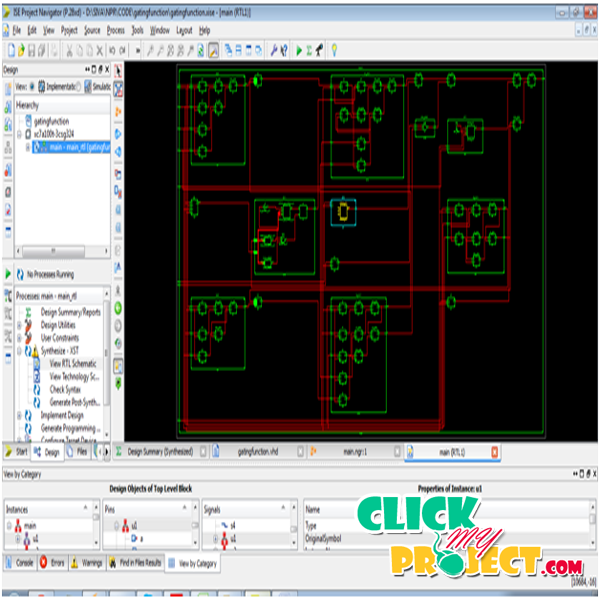

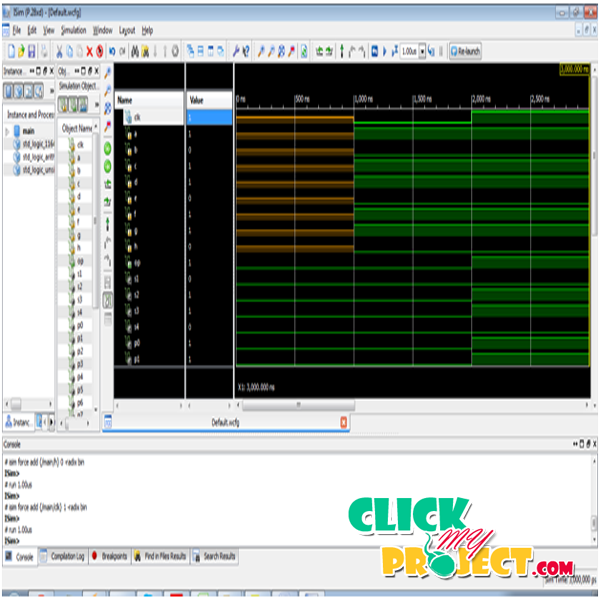

Clock gating is a popular technique used in many synchronous circuits for reducing dynamic power dissipation. This clock gating process can also save significant die area as well as power, since it removes large numbers of different muxes and replaces them with clock gating logic. For the duration of this method, a clock gating cell (CGC) is inserted, which covers an internal latch that filters out potential glitches from a block called as the gating function. This is achieved by matching factored forms of the gating functions with those of existing logic nodes, thus we call this technique as factored form matching. If use matching factor forms, it find the same pulse gate signals and use that signal and satisfy the same signal needed in tree structure. Strong matching identifies matches that are explicitly present in the factored forms, and weak matching seeks matches that are implicit in the logic and thus are more difficult to discover. We are exploring VLSI circuit and architecture techniques to instead minimize the joules-per-information in such communication, thereby achieving more energy-efficient communication. Our proposed work is WSA gating technique, This clock gating process can also save significant die area as well as power. The WSA technique to modify the gating function due to the flip flop architecture. This WSA technique to reduce the clocking signal and the gate pattern. Runtime is especially significant in circuits that contain many combinational gates and many flip-flop groups. We optimized clock gating function to be applied by the hierarchical tree function architecture. The modification of the factoring trees of gating functions so that more matches can be discovered and addressing the issue of computation time to improve scalability.