Low-Power Programmable PRPG With Test Compression Capabilities

₹3,500.00

10000 in stock

SupportDescription

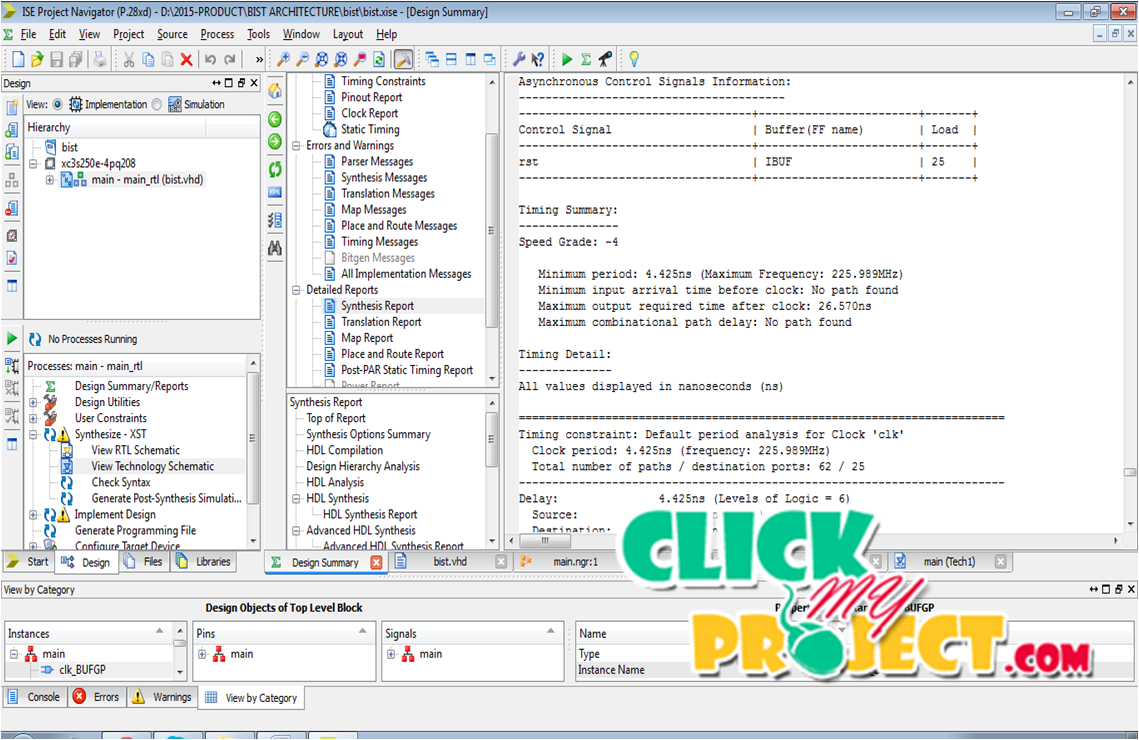

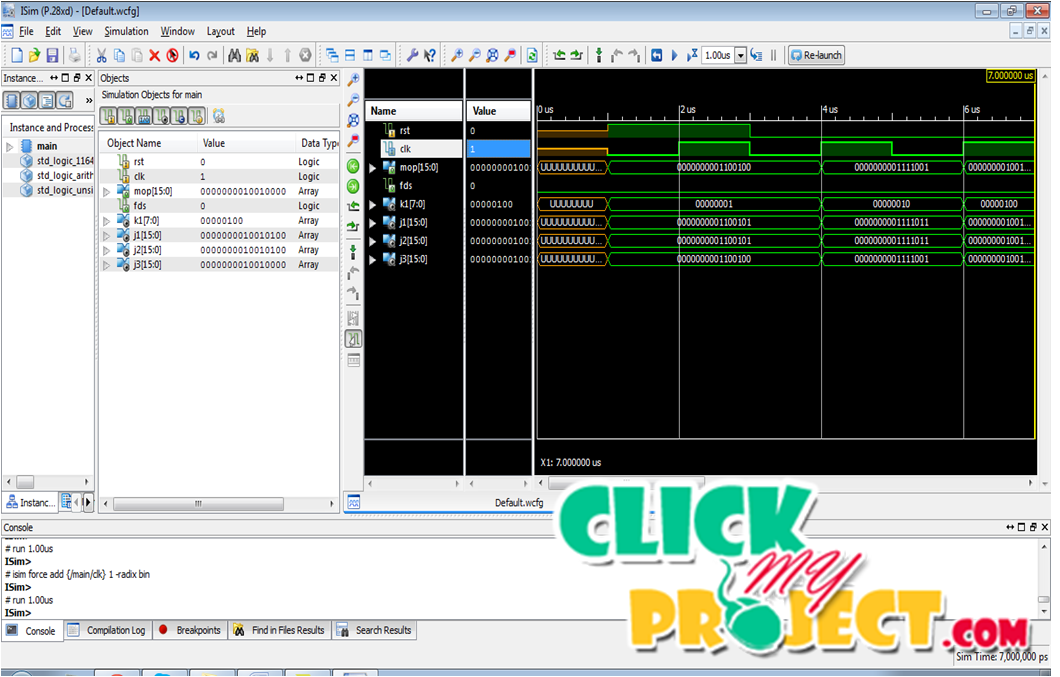

BIST (Build-in Self-Test), schemes are the solution of testing VLSI devices. BIST is used to make faster, less-expensive integrated circuit manufacturing tests. The IC has a function that verifies all or a portion of the internal functionality of the IC. In some cases, this is valuable to customers, as well. For example, a BIST mechanism is provided in advanced field bus systems to verify functionality. They perform during testing of circuits based on CTL. A cyclic redundancy check is an error-detecting code commonly used in digital networks and storage devices to detect accidental changes to raw data. The existing work is to design the low-power (LP) programmable generator capable of producing pseudorandom test patterns with desired toggling levels and enhanced fault coverage gradient compared with the best-to-date built-in self-test (BIST)-based pseudorandom test pattern generators. But it requires more limitation. So the proposed system is to design a LP-TPG based BIST architecture and to include the normalized Euclidean distance (NED) based CRC process. This process is used to identify the fault effectively and to optimize the test generation processing time. The proposed work is to modify test pattern generation scheme. The cyclic redundancy check (CRC) polynomial generation is to used to modify the sign generation work. This work is used to identify the fault location. The proposed system is to improve the BIST system performance level and to reduce the power consumption level also. The proposed system is used to increase the test pattern generation process. Our proposed work is to develop the VHDL programmable logic function and to simulate the XILINX 14.2 software.