Low Leakage TCAM for IP Lookup Using Two-Side Self-Gating

Our Price

₹3,000.00

10000 in stock

Support

Ready to Ship

Description

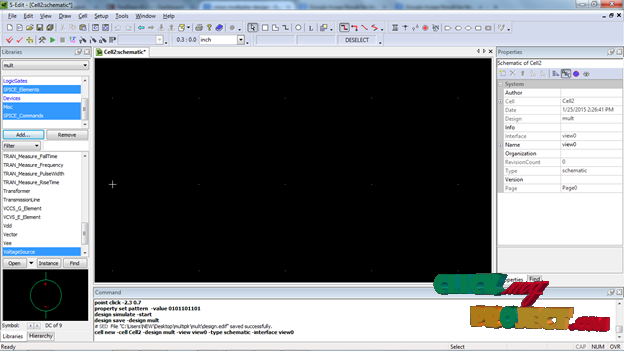

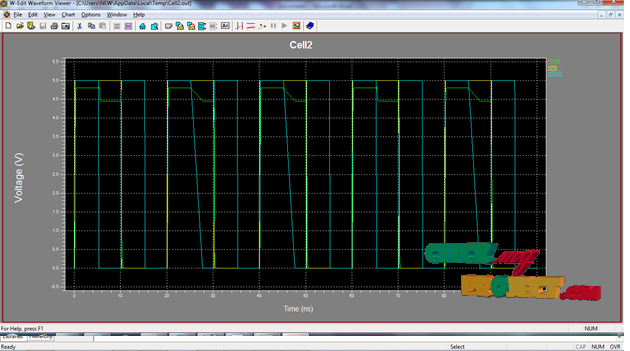

Ternary Content Addressable Memory (TCAM) is hardware based parallel lookup tables with bit-level masking capability. They are attractive for applications such as packet forwarding and classification in network routers. Holographic associative memory provides a mathematical model for “Don’t Care” integrated associative recollection using complex valued representation. In existing they Using traditional Ternary Content Addressable Memories(TCAMs) to perform high-speed packet classification has become the de facto standard in industry, Because traditional TCAMs can facilitate constant time classification by comparing a packet with all rules of ternary encoding in parallel. and a low leakage power TCAM architecture which uses two-side self-power gating technique is proposed to reduce the leakage power dissipation of the mask SRAM cells. Ternary content-addressable memory (TCAM) is a popular hardware device for fast routing lookup and an attractive solution for applications such as packet forwarding and classification. In our Proposed work, we develop Heterogeneous CMOS design system for low power in reading and writing process. This technique to improve the address searching process in TCAM architecture. To reduce the power consumption level compare to proposed system. This technique is mainly consider the leakage power reduction. In this architecture, we improve the power consumption level in TCAM architecture. To modify the two-side self power gating technique. Because it requires more power consumption. So we use the Heterogeneous CMOS design system. In this technique used to improve the power consumption level.

Tags: 2014, Domain > Network Projects