Intend and Implementation of Automatic V ending Machine using VHDL

Our Price

₹3,000.00

10000 in stock

Support

Ready to Ship

Description

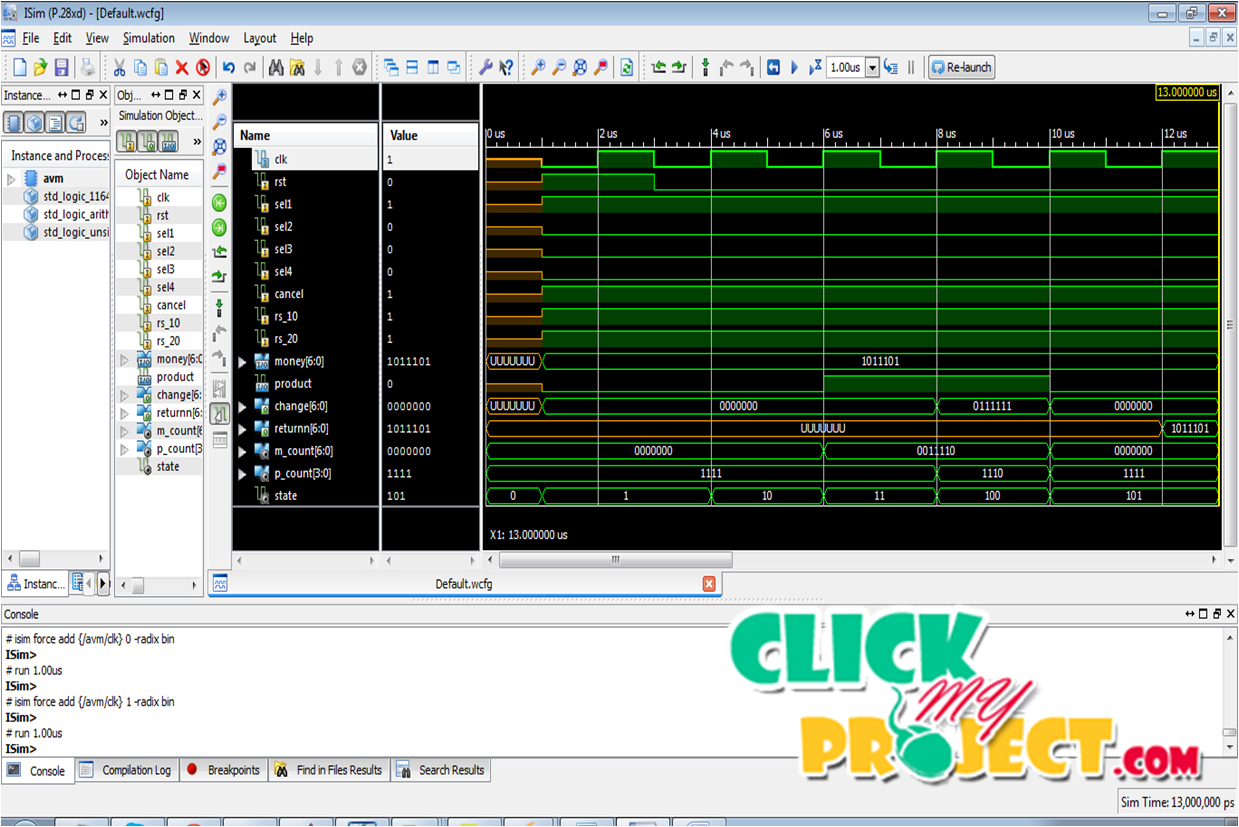

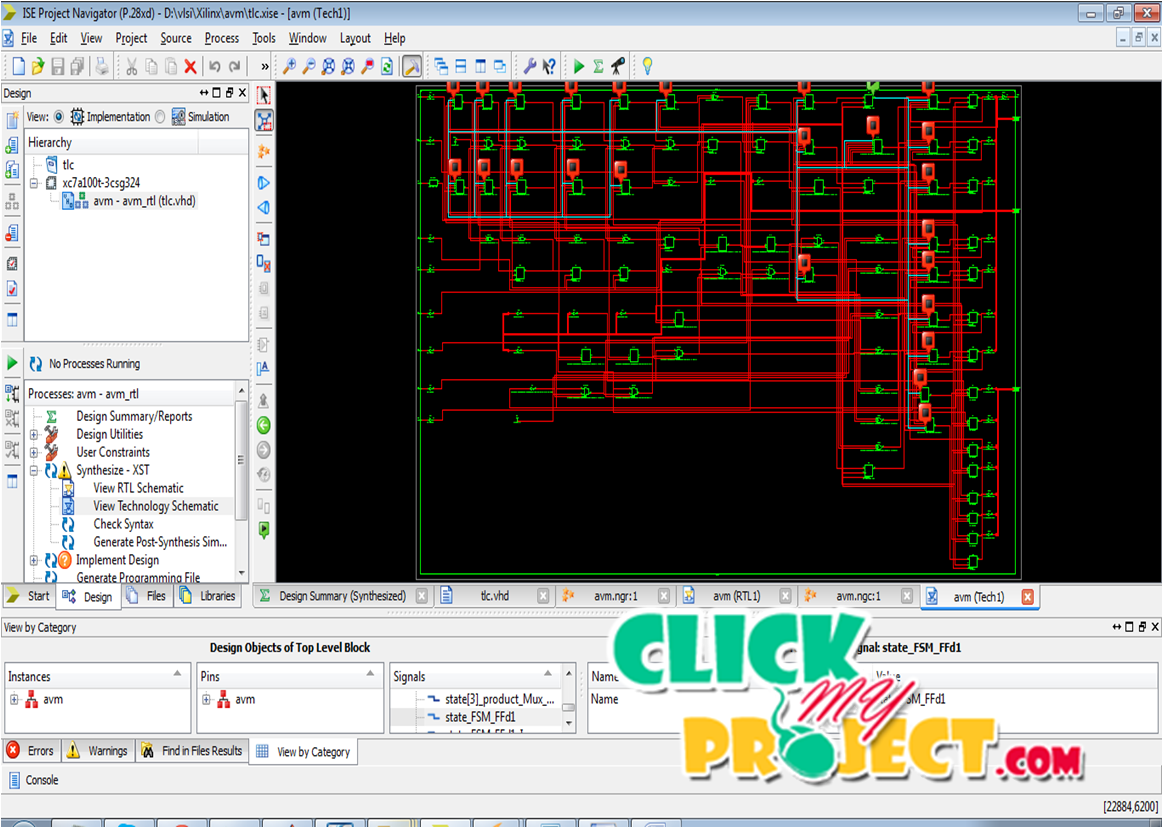

Design of area- and power-efficient high-speed data path logic systems are one of the most substantial areas of research in VLSI system design. The digital architecture is mainly used in all type of real world application architectures and thus the architecture to modified based on the enhancement purpose. Finite State Machine (FSM) modeling is the most crucial part in developing proposed model as this reduces the hardware. Vending machines are used to dispense small different products, when a coin is inserted. These machines can be implemented in different ways by using microcontroller and FPGA board. Here in this paper, we proposed an efficient algorithm for implementation of vending machine on FPGA board. Because FPGA based vending machine give fast response and usesless power than the microcontroller based vending machine. The FPGA based vending machine supports four products and three coins. The vending machine accepts coins as inputs in any sequence and delivers products when required amount is deposited and gives back the change if entered amount is greater than the price of product. A new approach is proposed to design an FSM based Vending Machine with auto-billing features. The machine also supports a cancel feature means that the person can withdraw the request and the money will be returned back to the user. The user will get a bill of total number of products delivered with total price. In a Finite State Machine the circuit’s output is defined in a different set of states i.e. each output is a state. A State Register to hold the state of the machine and a next state logic to decode the next state. An output register defines the output of the machine. In FSM based machines the hardware gets reduced as in this the whole algorith m can be explained in one process.

Tags: 2014, FPGA Projects, VLSI