Input Vector Monitoring Concurrent BIST Architecture Using SRAM Cells

Our Price

₹3,000.00

10000 in stock

Support

Ready to Ship

Description

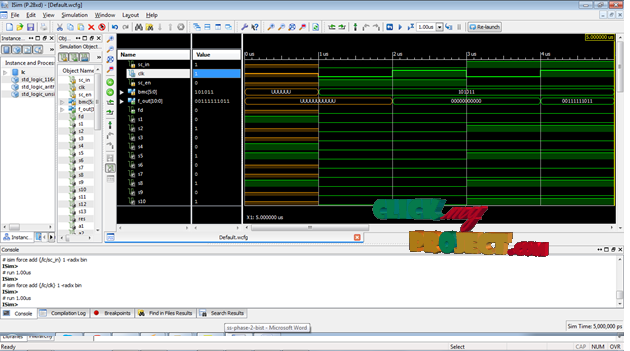

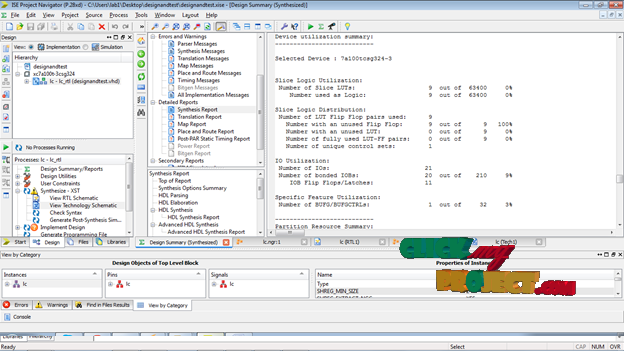

BIST (Build-in Self Test), schemes are the solution of testing VLSI devices. BIST is used to make faster, less-expensive integrated circuit manufacturing tests. The IC has a function that verifies all or a portion of the internal functionality of the IC. In some cases, this is valuable to customers, as well. For example, a BIST mechanism is provided in advanced fieldbus systems to verify functionality. At a high level this can be viewed similar to the PC BIOS’s power-on self-test (POST) that performs a self-test of the RAM and buses on power-up. They performs during testing of circuits based on CTL. A cyclic redundancy check is an error-detecting code commonly used in digital networks and storage devices to detect accidental changes to raw data. In the paper they proposed system, of BIST architecture designed using SRAM. Basically BIST techniques are two test modes, such as offline and online. Offline testing performs on either normal mode or test mode. In Square window monitoring concurrent BIST, During test of VLSI circuits, this concentrates on Concurrent test latency(CTL). In the design of BIST architecture performed using SRAM cells. In our proposed work we are going to implement Various Clock pattern based Design and this will give better performance on Concurrent test latency(CTL). That means the time required to complete the test.