Increase in Read Noise Margin of Single-Bit-Line SRAM Using Adiabatic Change of Word Line Voltage

₹3,000.00

10000 in stock

SupportDescription

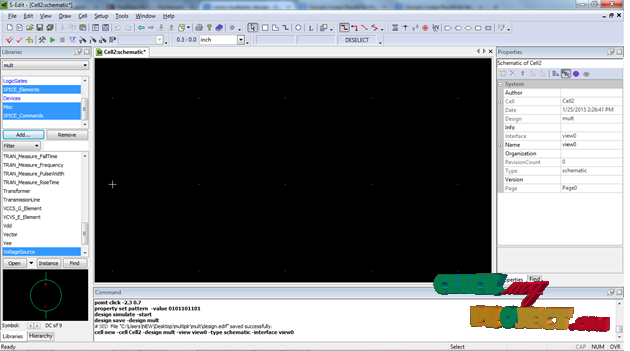

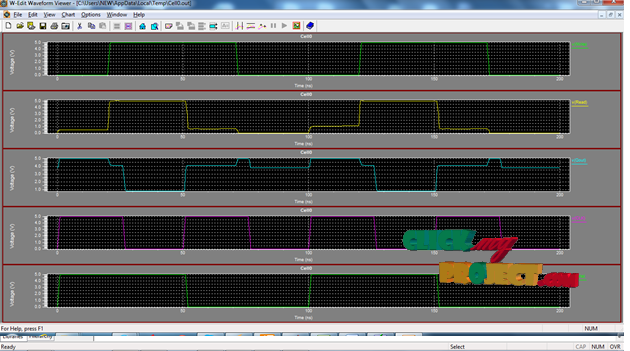

SRAM is basically used as data storage elements. In SRAM(Static RAM), During Read operation, Dynamic Noise Margin occurs. During Read operation, Adiabatic Charging occurs in word line. Which generates DNM. Low voltage performance used to reduce DNM. Hence in proposed we Introducing new SRAM architectures, which is smaller than conventional and previous. Hence by smaller design, power consumption reduced. Such data storage can be used for storage of state. Nonvolatile memories can get back stored information even when not powered. The most widely used form of primary storage today is a volatile form of random access memory (RAM), meaning that when the computer is shut down, anything contained in RAM is lost. However, most forms of non-volatile memory have limitations that make them unsuitable for use as primary storage. In Existing they were proposed the design Conventional SRAM has 2 pre-charged BL. Single BL SRAM uses only one Bit-Line for read operation. Adiabatic circuits are low power circuits which use “reversible logic” to conserve energy. Hence they proposed Single bit line SRAM design. Because single bit line design has larger Static noise margin than Two-BL SRAM. Which provides high speed, low power. The existing design need reduced size SRAM design. But by shared ports in circuit, leakage occurs. Which also consumes power. Hence in their proposed work concentrated to reduce the power consumption and area efficiency. Here, we propose a design SRAM using CMOS technology. CMOS technology provide less noise ration during design. The proposed SRAM design is based on Hetero junction CMOS technology. Which performs, possible data store and restore operations.