FPGA based fast and high-throughput 2-slow retiming 128-bit AES encryption algorithm

₹3,000.00

10000 in stock

SupportDescription

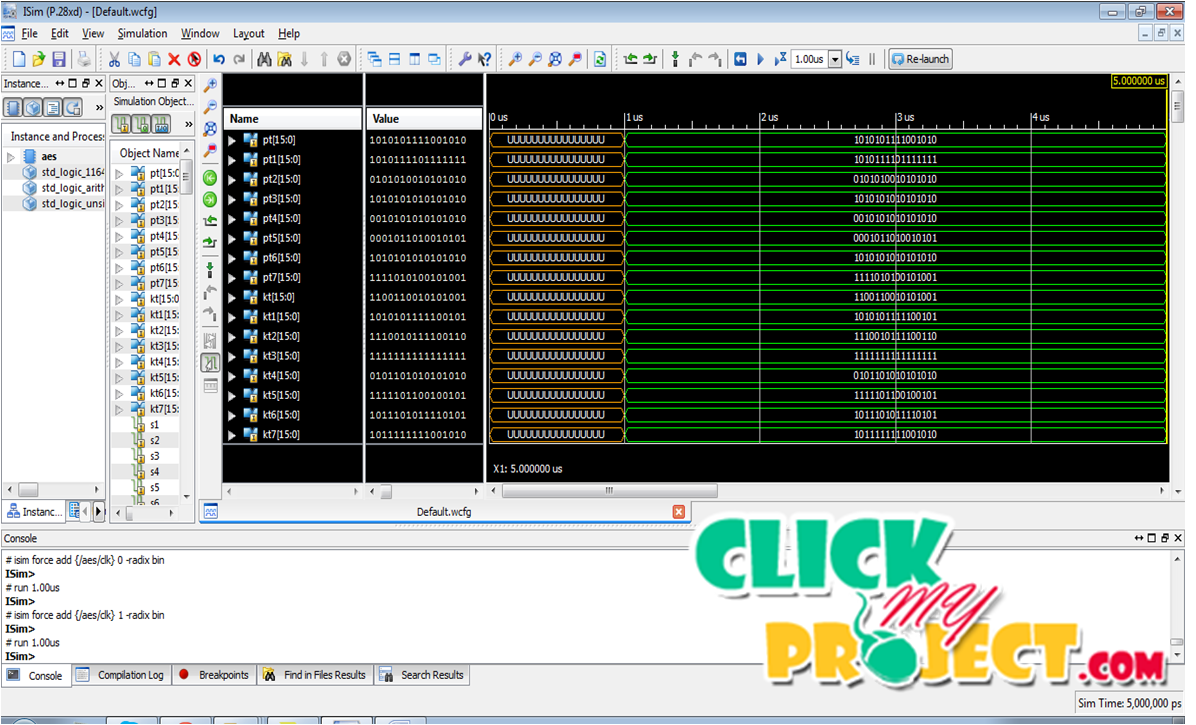

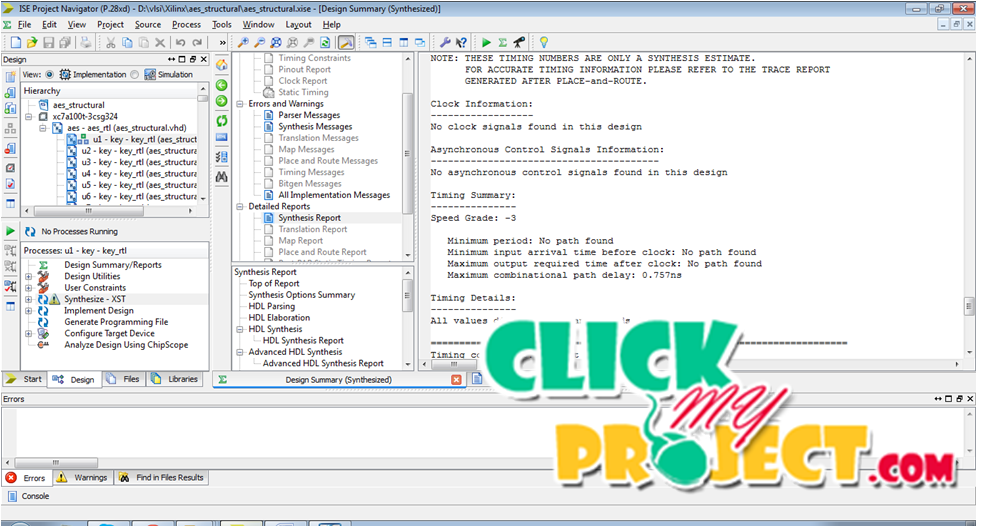

A high throughput digital design of the 128-bit Advanced Encryption Standard (AES) algorithm based on the 2-slow retiming technique on FPGA. Architecture of the AES algorithm is implemented in the gate level by high-speed and breakable structures that are desirable for the 2-slow retiming. The Mix-columns transformation is implemented based on multiplication by constants 2 and 3 modules with combinational logic circuits. The AES key expansion algorithm takes as input a 4-word key and produces a linear array of 44 words. Each round uses 4 of these words . Each word contains 32 bytes which means each subkey is 128 bits long. pseudocode for generating the expanded key from the actual key.