Economizing TSV Resources in 3-D Network-on-Chip Design

₹3,500.00

10000 in stock

SupportDescription

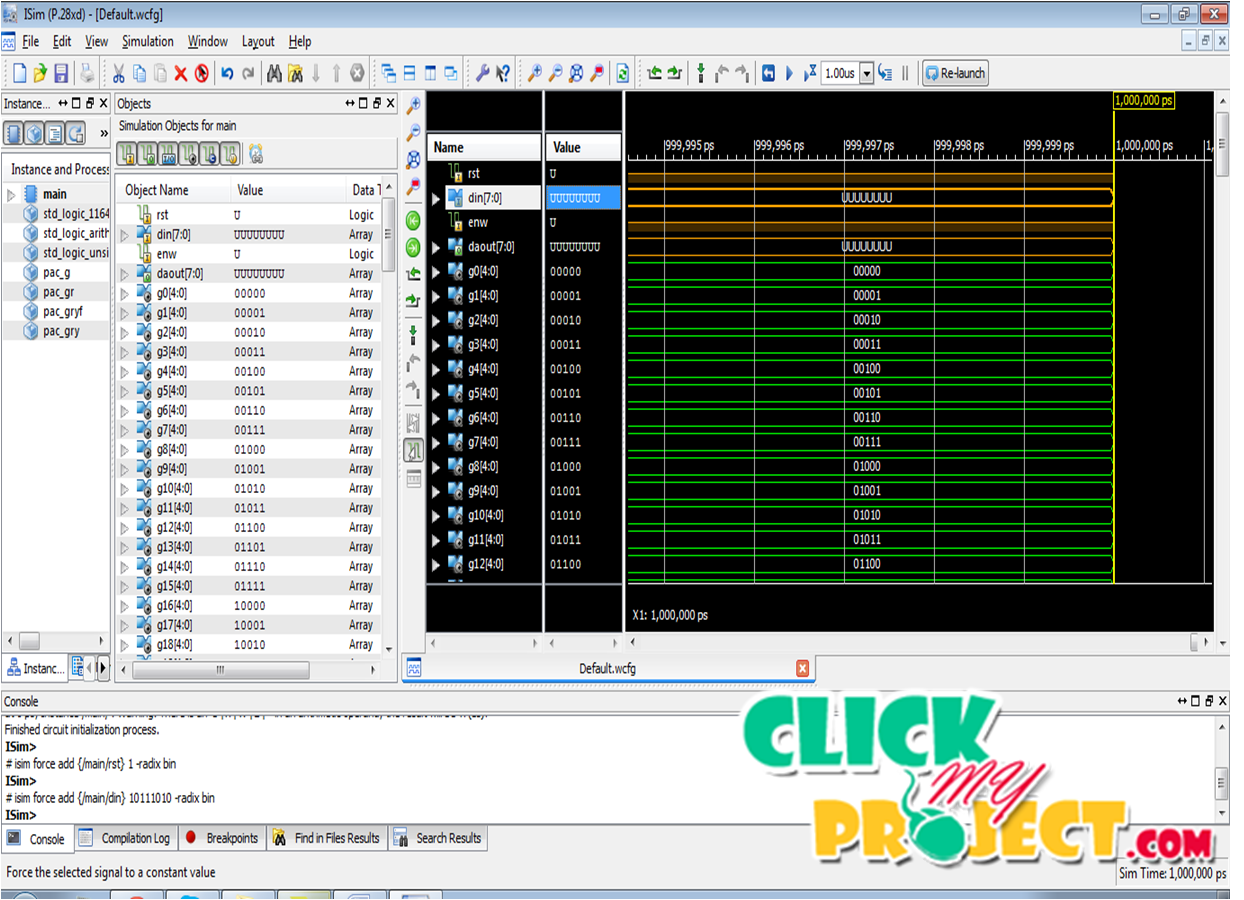

Three dimensional Networks-on-Chip (3D NoCs) have attracted a growing interest to solve on-chip communication demands of future multi-core embedded systems. However, 3D NoCs have not been completely accepted into the mainstream due to issues such as the high cost and complexity of manufacturing 3D vertical wires, larger memory, and area and power consumption of 3D NoC components than that of conventional 2D NoC. Network-on-Chip (NoC) has been proposed as a more promising solution and has gained the attention of many researchers in this field of study. NoCs adopt links, switches and packet or circuit switching to handle data communication in a multi-core system. Existing system utilize general purpose platform SIMICS to abstract traffic. This method cannot ensure two simulation systems strict consistency. In this project the system proposed a complete design framework of a Distributed Shared Memory homogenous multi-core system based on 3D Torus interconnects. The proposed system used for practical experiments. The proposed system achieve lower area and power consumption of on-chip communication components with a minimal performance trade-off.