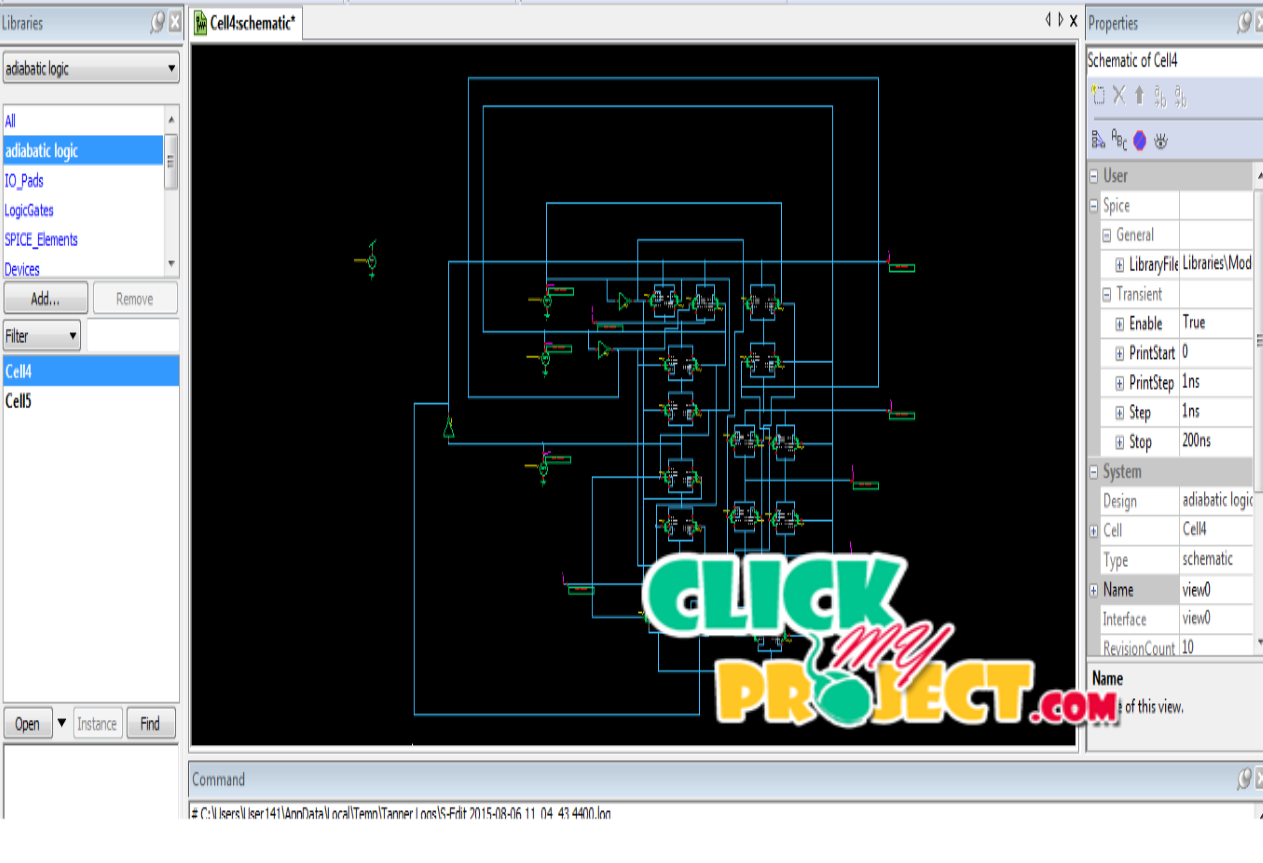

Design of Adiabatic Dynamic Differential Logic for DPA Resistant Secu re Integrated Circuits

₹3,500.00

10000 in stock

SupportDescription

The influence of electronics in pervasive computing needs confidentiality of the electronically processed and transmitted data. The threat of DPA attacks is of crucial importance when designing cryptographic hardware. As a result, several DPA counter-measures at the cell level have been proposed in the last years, but none of them offers perfect protection against DPA attacks. Moreover, all of these DPA-resistant logic styles increase the power consumption and the area consumption significantly. On the other hand, there are some logic styles which provide less power dissipation (so called charge recovery logic) that can be considered as a DPA countermeasure. Security of electronic data remains the major concern. Although the power minimization has become a primary concern in VLSI design methodologies, it is not the most important factor in many cases. For example, security is the main goal when designing cryptographic hard ware. The implementation of ultra-low power digital system is increased in now-days to provide low digital system the sub threshold adiabatic logic circuits are used. Thus this type of adiabatic logic is providing low power consumption. The adiabatic logic reduces the power consumption and it is used in low power VLSI circuits.