Area Efficient Parallel Fir Digital Filter Structure For Symmetric Convolution Based On Fast Fir Algorithm

₹3,000.00

10000 in stock

SupportDescription

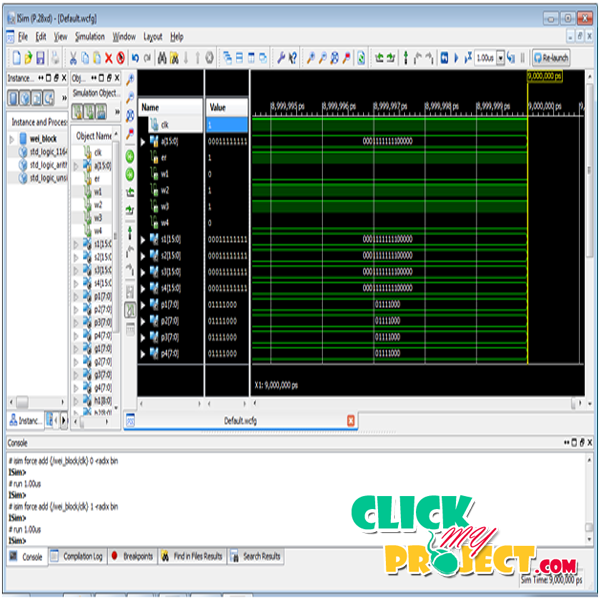

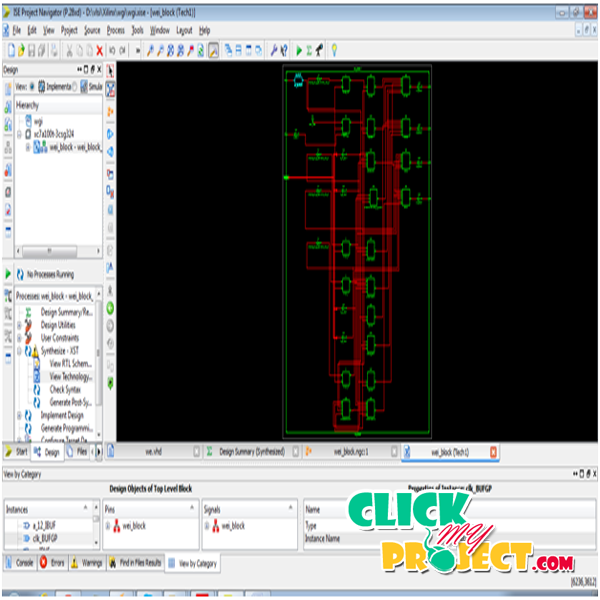

The filter process mainly used to DSP and DIP real world application. The filter process to remove the noise in original signal or image. So the filter architecture optimized process, to reduce the filter processing time and to increase the performance. Adaptive digital filters find wide application in several digital signal processing (DSP) areas. The DA based FIR filter architecture reduce the hardware complexity and reduce the LUT count in RAM block. The ASIC based technology to modify the filter architecture level. The filter architecture mainly focused by the addition process and to optimize the carry selection time. So we use the carry save adder architecture. The filter architecture to increase the system speed and to improve the system performance level. The distributed based RAM design is proposed to the FPGA architecture. In this architecture, the proposed method used to design DA based FIR filter architecture. And this architecture reduce the hardware complexity and also reduce the carry propagation due to the filtering process. This paper presents the modified delayed LMS adaptive filter consists of Weight update block with Partial Product Generator (PPG) to achieve a lower adaptation delay and efficient area, power, delay. To achieve lower adaptation delay, initially the transpose form LMS adaptive filter is designed but the output contains large delay due to its inner product process. Here, the pipelining structure is proposed across the time consuming combinational blocks of the structure to reduce the critical path. From the simulation results, we find that the proposed design n offers large efficient output comprises the existing output with large complexities.. We use the digital architecture based VLSI technology to modify the FIR filter architecture. In this architecture, For achieving lower adaptation-delay and area-delay-power efficient implementation, we use a novel partial product generator and to modify the efficient architecture for the implementation of a delayed least mean square adaptive filter using FIR algorithm. This DA-based FIR filter architecture to develop the VHDL language using XILINX 14.2 software.