A Short-Channel-Effect-Degraded Noise Margin Model for Junctionless Double-Gate MOSFET Working on Subthreshold CMOS Logic Gates

Our Price

₹4,500.00

10000 in stock

Support

Ready to Ship

Description

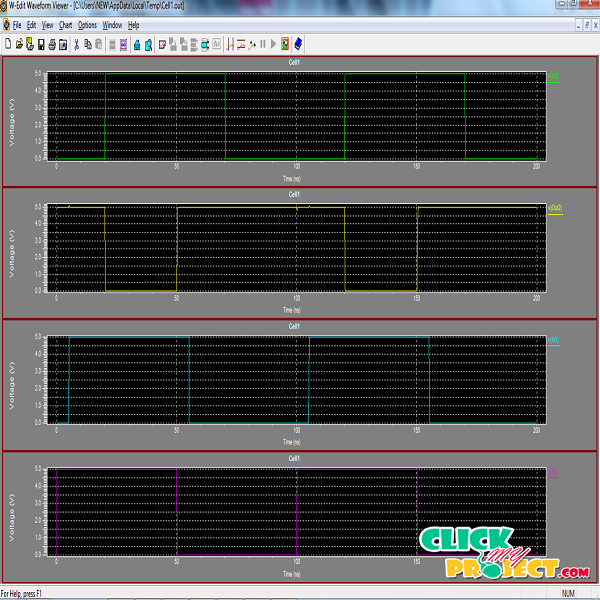

Based on the device and equivalent transistor model, we present a short-channel-effect (SCE)-degraded noise margin (NM) model for junctionless double-gate MOSFET working on subthreshold CMOS logic gate. The device parameters such as the thick silicon thickness, thick gate oxide thickness, high doping density, and short channel length can severely degrade the NM due to serious SCE. By contrast, both the small subthreshold slope ? and the balanced transistor strength S can suppress the NM degradation more efficiently.