A Scalable and Modular Architecture for High-Performance Packet Classification

₹3,000.00

10000 in stock

SupportDescription

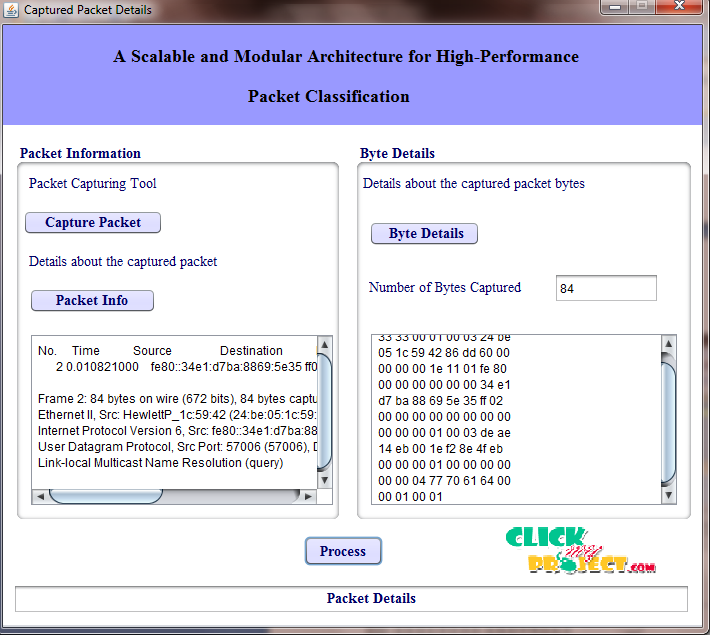

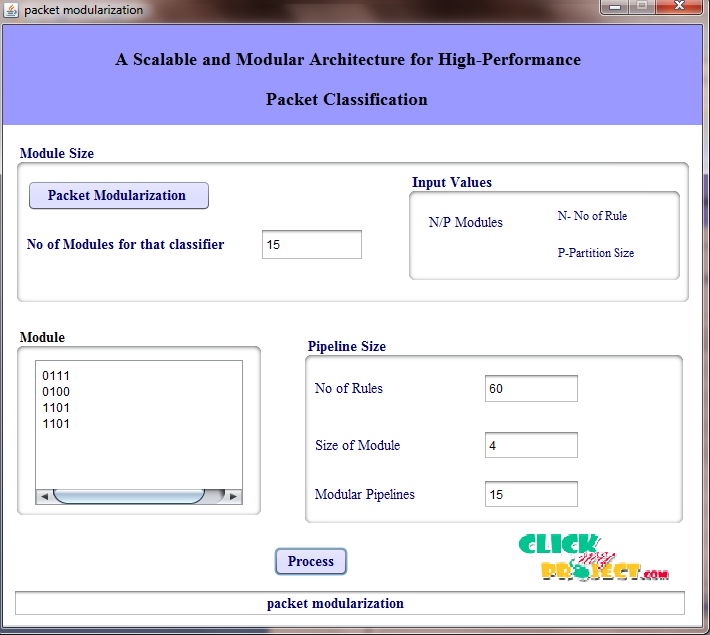

Packet Classification is one of the core function in network infrastructure for various purposes. Performing wire Speed packet classification is challenging with the increasing throughput demands in modern networks. Also the performance of today packet classification solutions depends on the characteristics of classifier. To perform packet classification, one or more header fields of an incoming packet is checked against a set of predefined rules. In this work, we propose a novel modular Bit-Vector(BV) based architecture to perform high-speed packet classification on Field Programmable Gate Array(FPGA). FPGA offers reconfigurability and deliver high performance due to the custom built nature of the architecture. This platform is widely used in network application to implement multi-gigabit packet forwarding engines. We introduce an algorithm named StrideBV and Modularize the BV architecture to achieve better scalability than traditional BV methods. Further, we incorporate the range search in our architecture to eliminate range to prefix conversion. The post place-and-route results of our implementation on a state-of-the-art Field Programmable Gate Array shows that the proposed architecture is able to work at 100+Gbps for minimum size packets while supporting large ruleset up to 28K rules using only the on-chip memory resources. Our solution is ruleset-feature independent. That means the above performance can be guaranteed for any ruleset regardless of the composition of the ruleset.