A Parallel Digital VLSI Architecture for Integrated Support Vector Machine Training and Classification

US$40.46

10000 in stock

SupportDescription

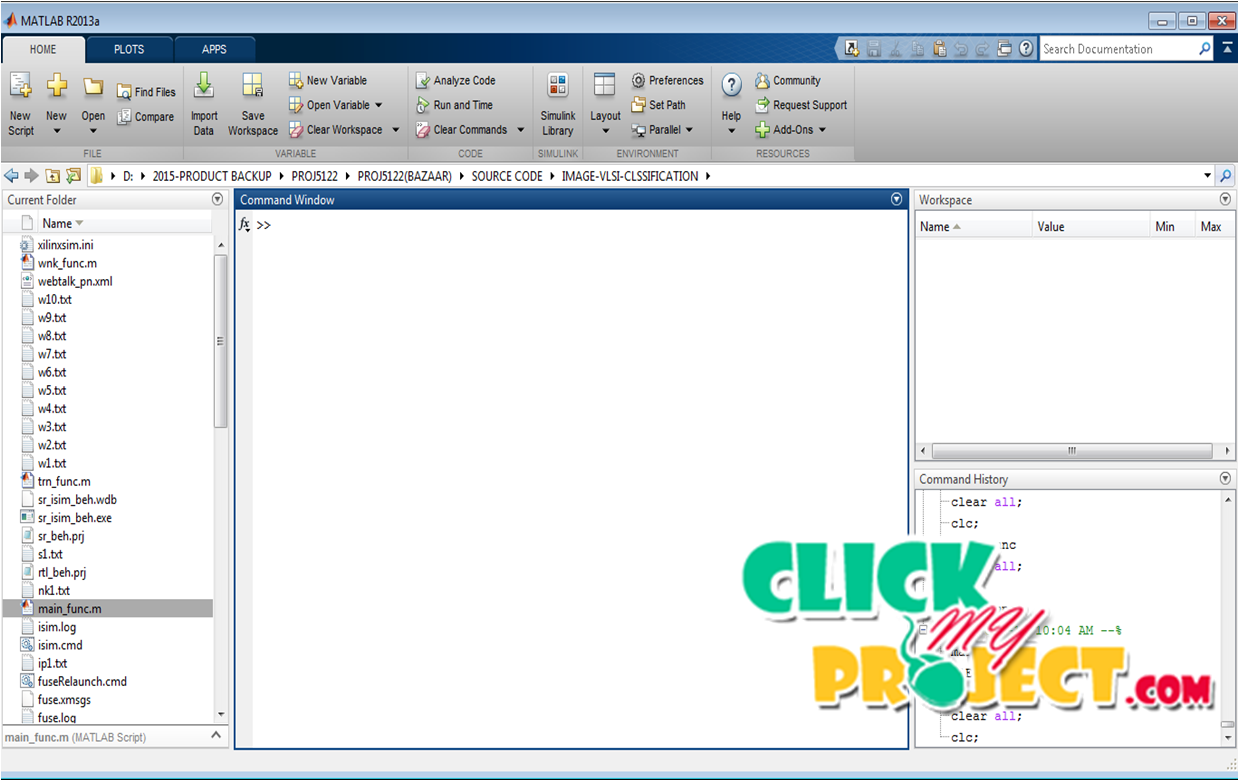

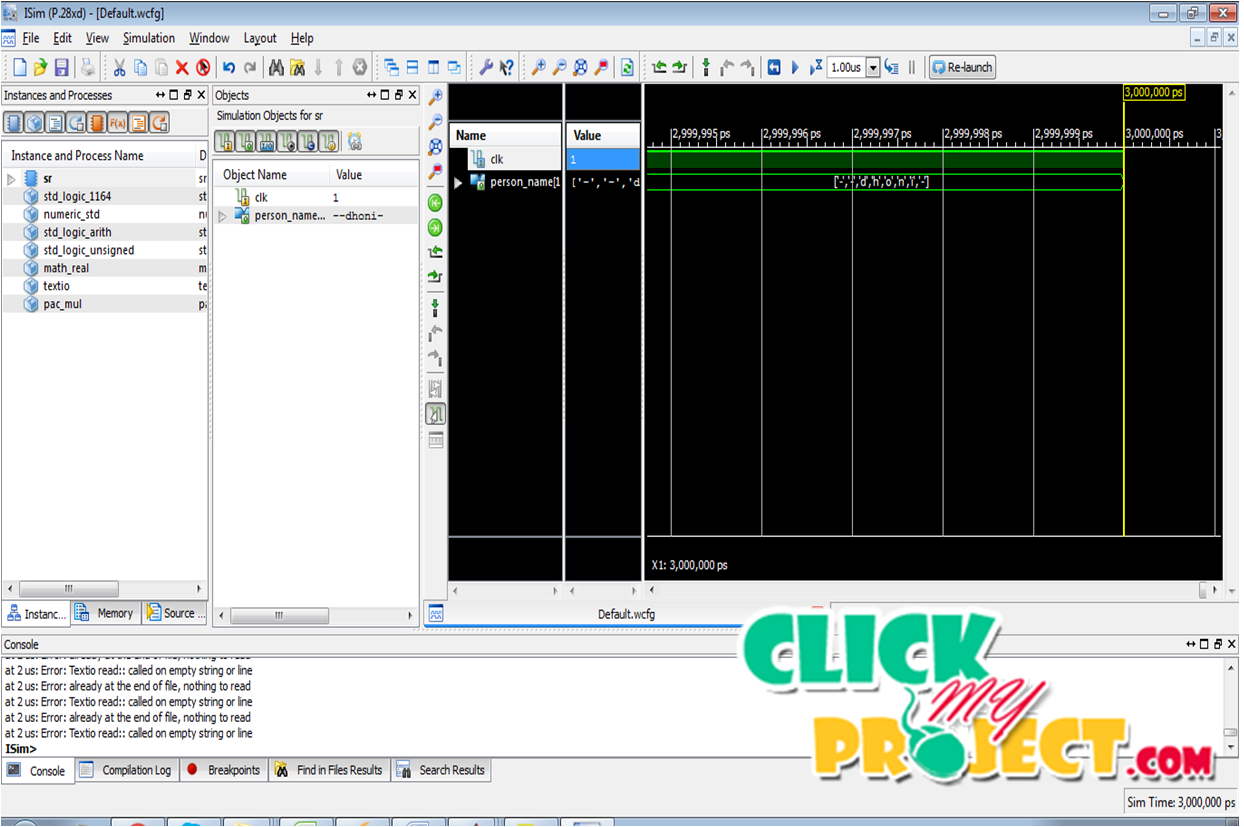

Driver fatigue is a significant factor in a large number of vehicle accidents. Thus, driver drowsiness detection has been considered a major potential area so as to prevent a huge number of sleep induced road accidents. Driver fatigue is a significant factor in a large number of vehicle accidents. Fatalities have occurred as a result of car accidents related to driver inattention, such as distraction, fatigue, and lack of sleep. Studies and experiments have substantiated the fact that driving performance deteriorates with increased drowsiness. VLSI based DIP systems are to modify the internal circuit structure level and to optimize the circuit complexity level and to improve the system quality. Most digital image processing algorithms are specified with floating-point data types but they are finally implemented in fixed-point architectures in order to satisfy the cost and power consumption constraints of embedded systems. Our proposed work is to design a efficient VLSI architecture based digital image processing feature extraction (LBP + DFT) and classification (SVM) system using RPR truncation multiplier architecture. This work is to identify the face image and update person details effectively. Existing system is to design a VLSI based SVM classifier architecture. This architecture is used to effectively identify the disease types. Proposed system is to design a (LBP + DFT) feature extraction architecture and conventional neural network classifier architecture. Then to design SVM classifier VLSI architecture and to optimize the normal processing element and exponential processing element design. Then to apply the CORDIC function based shift and rotation architecture and to analysis the threshold function level between support and test vector data base face image. Finally to identify the face image type effectively and to calculate the VLSI architecture delay time, speed and power consumption level. This work is to optimize the circuit complexity level. Our proposed work is face images feature extraction and classification application process. This application uses person details identification process for this project. The proposed system is to increase the system speed for real time DIP application.