A High-Throughput VLSI Architecture for Hard and Soft SC-FDMA MIMO Detectors

₹3,500.00

10000 in stock

SupportDescription

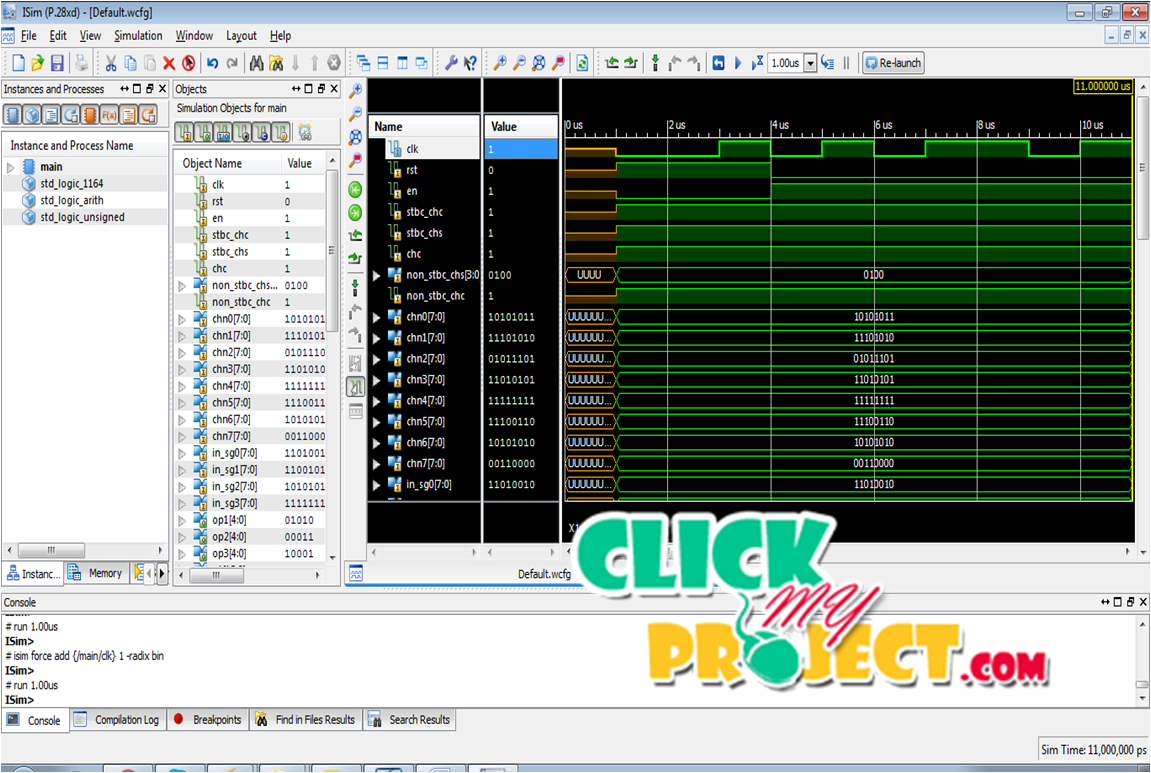

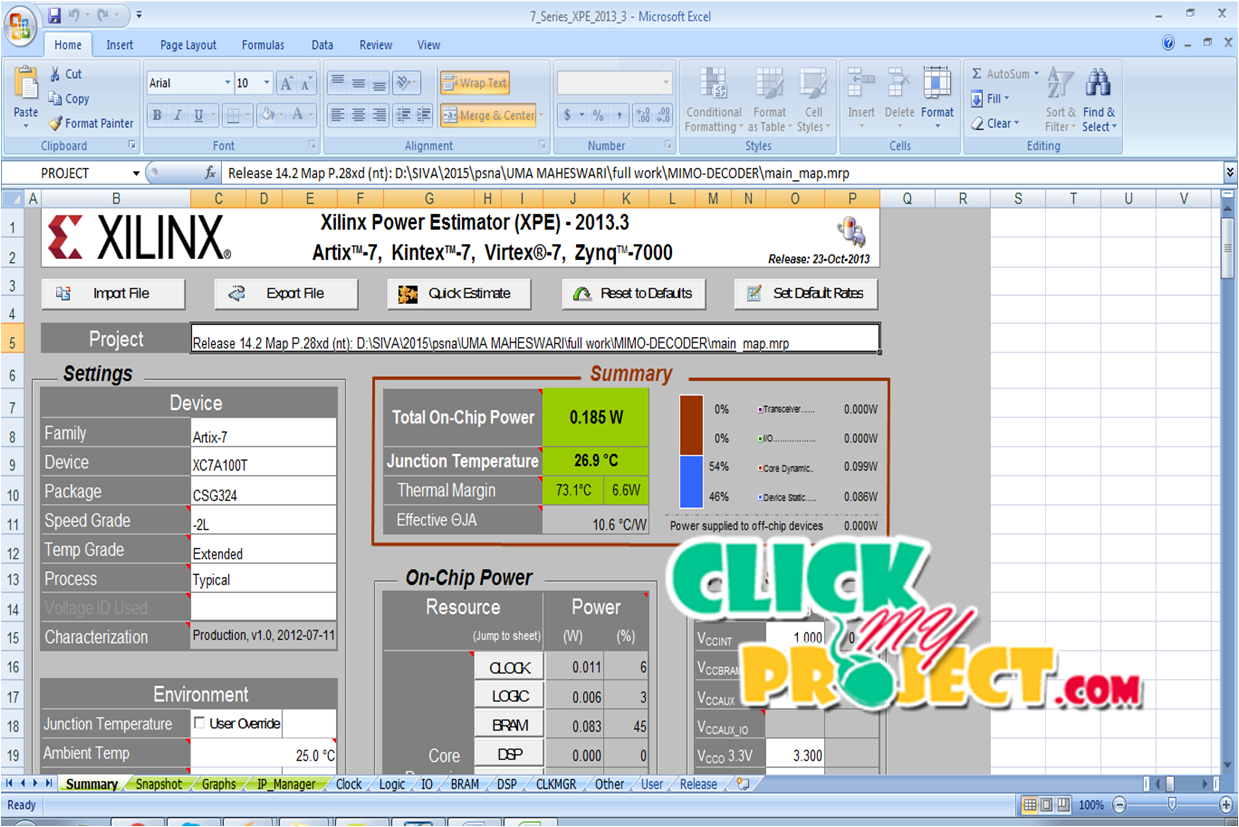

Now a days, the communication industry field is mainly focused by high data transfer and more channel capacity in mobile communication. MIMO-OFDM is the foundation for most advanced wireless local area network (Wireless LAN) and mobile broadband network standards. The efficient architecture of 4*4 16-QAM MIMO detectors are mainly used for the wireless communication. An area-efficient symbol detector is proposed for multiple-input multiple-output (MIMO) communication systems with reduced buffer memory architecture. Single-carrier FDMA (SC-FDMA) is a frequency-division multiple access scheme. It is also called Linearly precoded OFDMA (LP-OFDMA). Like other multiple access schemes (TDMA, FDMA, CDMA, OFDMA), it deals with the assignment of multiple users to a shared communication resource. SC-FDMA can be interpreted as a linearly precoded OFDMA scheme, in the sense that it has an additional DFT processing step preceding the conventional OFDMA processing. In this project system designed a low-complexity multiple-input multiple-output (MIMO) detector tailored for single-carrier frequency division-multiple access (SC-FDMA) systems. It is very suitable for efficient hardware implementations. In this architecture, our work is to design SC-FDMA MIMO received signal detector architecture using Euclidean distance technique. Our work is to modify the internal mimo detector architecture and to improve the architecture performance level. The existing K-BEST mimo detector architecture is mainly used to the communication process. The signal is to be transmitted through multiple input and multiple output sections. Existing K-BEST detection process time is to be increased. So the system performance is to be low. And the existing K-BEST mimo architecture is require more area.Proposed system is to design a uses single-carrier frequency division-multiple access (SC-FDMA) for multiple-input multiple-output (MIMO) detector using MMSE and ED technique. This technique is to optimize the symbol detector circuit complexity level using the two-way sorting approach. It can achieve the BER performance about 64-QAM mimo architecture. Proposed system is to increase throughput value and to reduce the latency level. Proposed system is to reduce the power consumption level for channel allocation process.