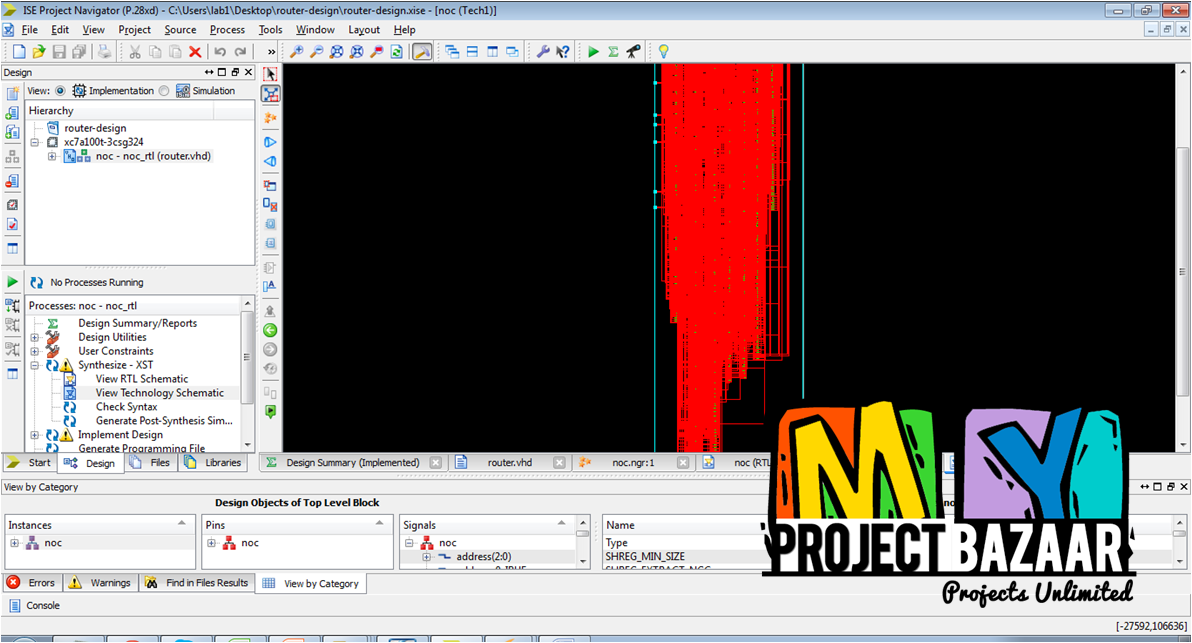

A graph based algorithm to minimize total wire length in vlsi channel routing

₹3,000.00

10000 in stock

SupportDescription

The important problem in VLSI layout design is minimization of total wire length. Minimization of wire length reduces Cost of physical wiring Electrical hazards -Power consumption and propagation delays Develop an efficient heuristic algorithm to reduce the wirelength. The routing scheme used in the NoC c an be either static or dy namic i n n ature. In static routing , one or more paths are selecte d for the tr afficflowsintheNoCatdesigntime. In the case of dy namic routing , the paths are selec te d based on the cur rent t r affic char a c ter istics of the networ k. Due to its s implicit y a nd the fac t that a pplication t r afficcan be well ch ar ac ter ize d for most SoC desig ns, static routing is w idely employed for NoCs. When compared to static sing le-path routing , the static multipath routing scheme improves path diversit y, there by minimizing networ k congestion a nd t r af-fic bottlenecks. Wh en the NoC is pre desig ned, w ith the NoC hav ing a fi xe d op er a ting frequency, data w idth, and h ence bandw idth ( bandw idth available on each networ k l ink is the produc t of the link data w idth a nd the NoC op er a ting fre-quency), re ducing congestion re sults in improved networ k per for mance. For most S oC desig ns, the NoC oper a ting fre-quency can b e s et to match the application requirements