A Fully Digital Front-End Architecture for ECG Acquisition System With 0.5 V Supply

Our Price

₹4,500.00

10000 in stock

Support

Ready to Ship

Description

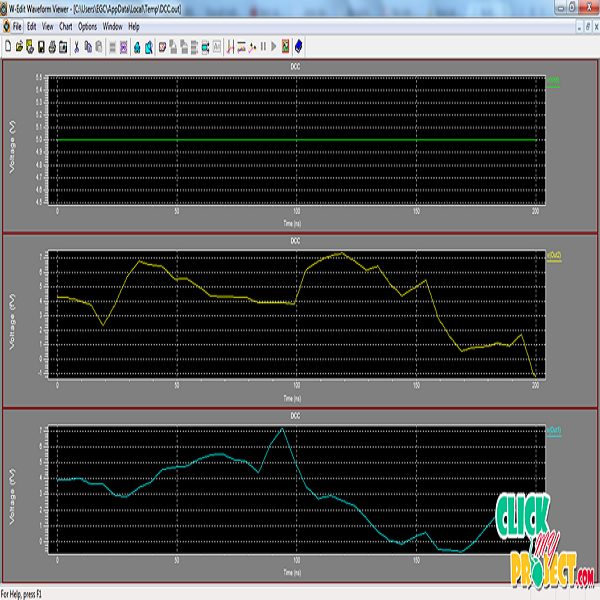

A new power-efficient electrocardiogram acquisition system that uses a fully digital architecture to reduce the power consumption and chip area. The proposed architecture is compatible with digital CMOS technology and is capable of operating with a low supply voltage of 0.5 V. In this architecture, no analog block, e.g., low-noise amplifier (LNA), and filters, and no passive elements, such as ac coupling capacitors, are used. A moving average voltage-totime converter is used, which behaves instead of the LNA and antialiasing filter.