A Fault Tolerant Technique Using Quadded Logic and Quadded Transistors

₹3,500.00

10000 in stock

SupportDescription

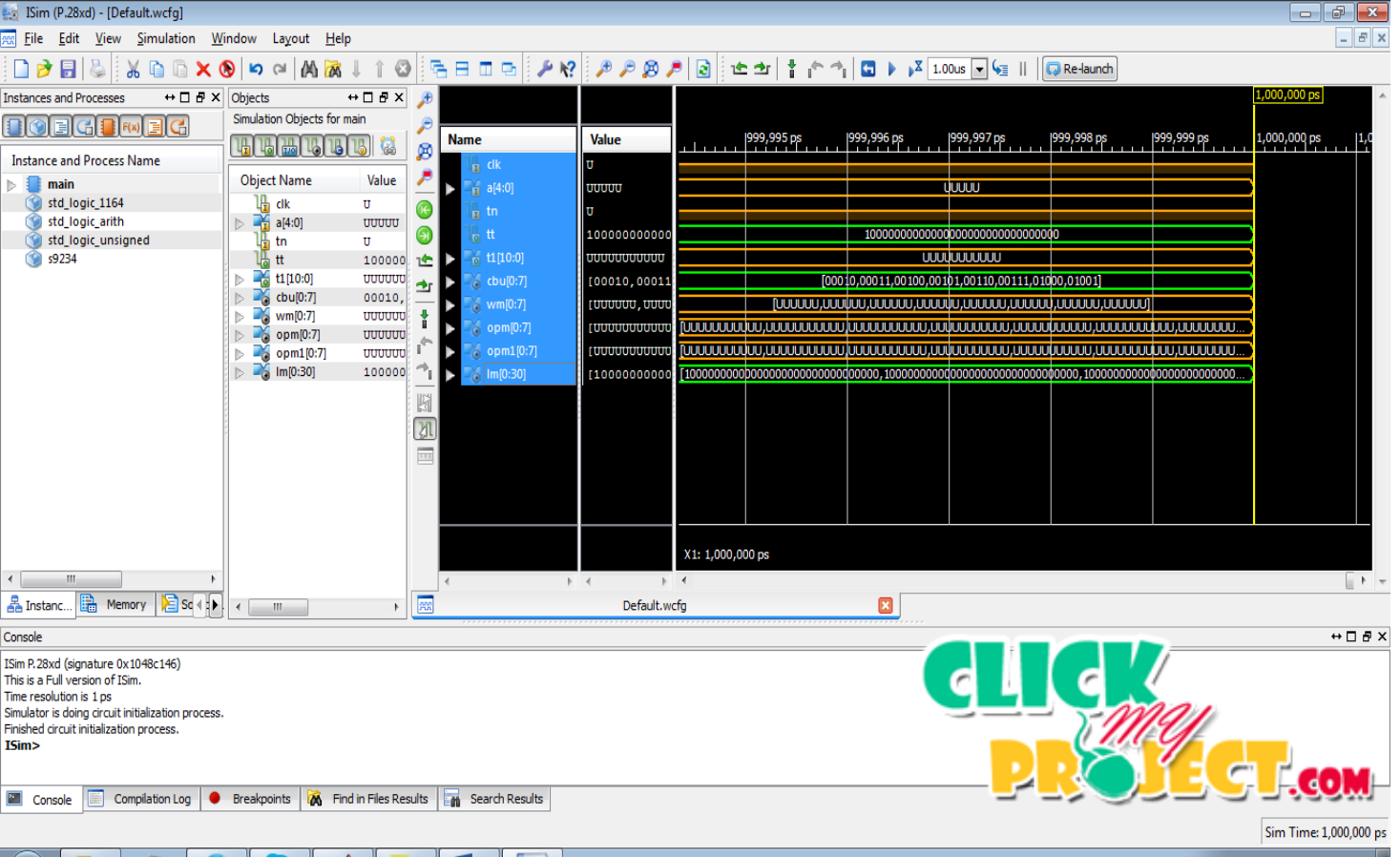

Now a days, core processor consists of more no of complex digital architecture. This architecture is consume more circuit area and power. This type of core processor is used to many applications and to improve the application performance level. But it have some problem due to circuit complexity level. Real time application internal core processors are need more time. So it occurs more error for internal core architecture output results. Our work is to design the low-power TAM based benchmark circuit testing architecture. This work is to identify the fault output, then to detect the fault location and to correct the fault in final output. This process is to improve the circuit vise testing performance. Proposed system is to design a benchmark circuit testing architecture using output data bit vector monitoring process. This technique is used to test the all internal core architecture for parallel form. This work is to implement the test pattern creation and to apply randomly. This process is to analysis the separate core internal architecture output result values. Proposed system is to modify the majority selection process and fault identification comparison process between expected test response and present test response results and correct the fault. The proposed system is to improve the TAM system performance level and to reduce the power consumption level also. The proposed system is used to increase the test pattern generation process. It reduce overall circuit complexity level and high reliability. This work is most suitable for multi core testing process.