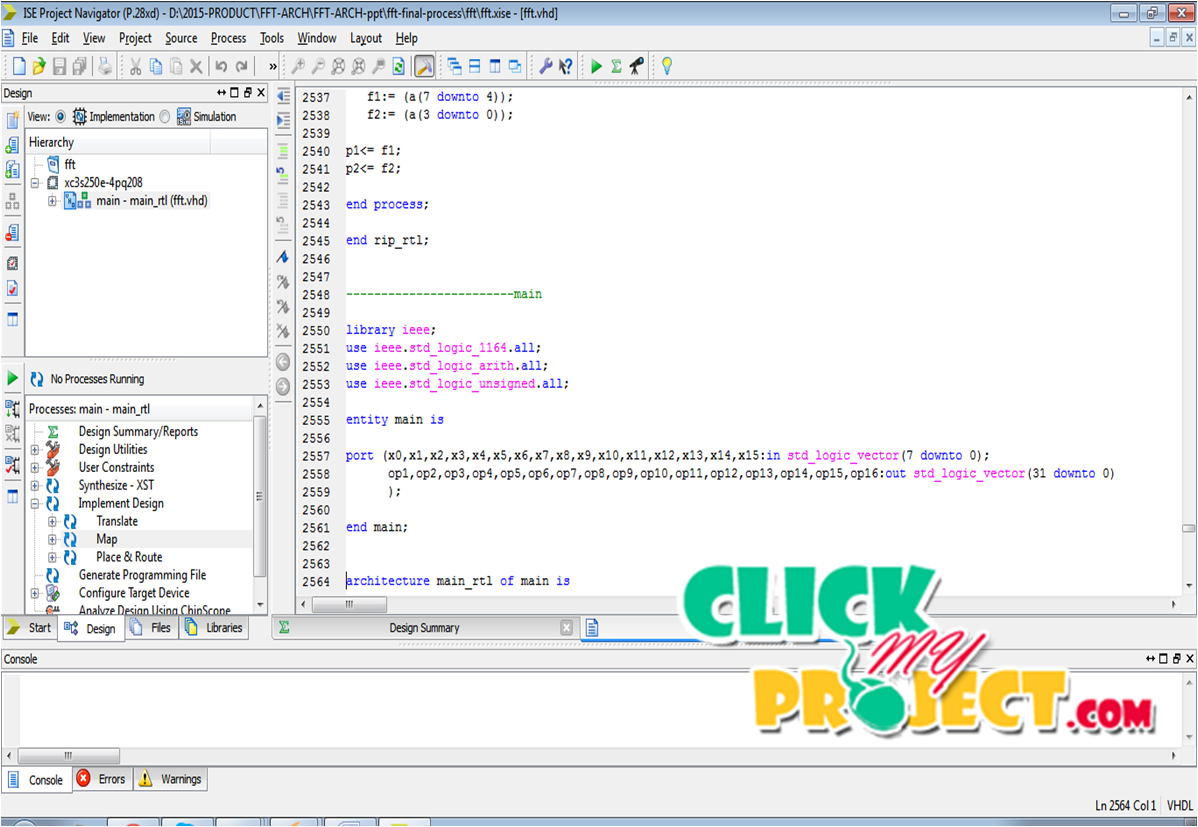

A Combined SDC-SDF Architecture for Normal I/O Pipelined Radix-2 FFT

Our Price

₹3,500.00

10000 in stock

Support

Ready to Ship

Description

Now a days, the MIMO-OFDM communication industry field is mainly focused by high data transfer and more channel capacity in mobile communication. VLSI technology is used to modify the any type digital based hardware architecture and to reduce the hardware system power, speed and complexity level. The real time pipelined FFT architectures have mainly been adopted to address the difficulties due to their attractive properties, such as small chip area, high throughput, and high speed operation. Our proposed work is to design the vlsi architecture based radix-2 based FFT architecture. The proposed SDF-SDC based FFT method is to require less no of multiplier architecture and to improve the real time DSP applications. The existing system is to design the split radix based FFT architecture. This architecture is to consist of more no of multiplier architecture, so it affects the system performance level. The proposed system is to a ADAPTIVE SPLIT variable length based 16-point FFT architecture. This architecture is to reduce the register and bit reviser element. This ADAPTIVE SPLIT design transform process is to maintain the self optimizing approach and to implement the high performance based arithmetic operator architecture. These architectures are is to perform the real and complex binary operation in 16-Point FFT adder, subtractor, parallel multiplier section. Then to increase the data rate for FFT transform function and to analysis the critical path functional level. Finally is to improve the weighted section performance level and to improve the constant multiplier functional level. This system is to reduce the circuit complexity level and to consume less power.

Tags: 2015, Digital Image Processing, VLSI