1.2 V 10-bit 75 MS/s Pipelined ADC With Phase-Dependent Gain-Transition CDS

₹3,000.00

10000 in stock

SupportDescription

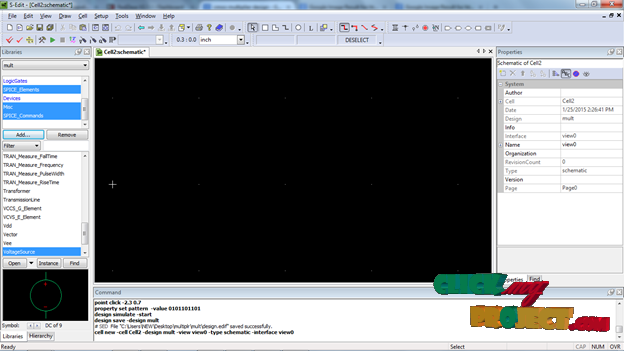

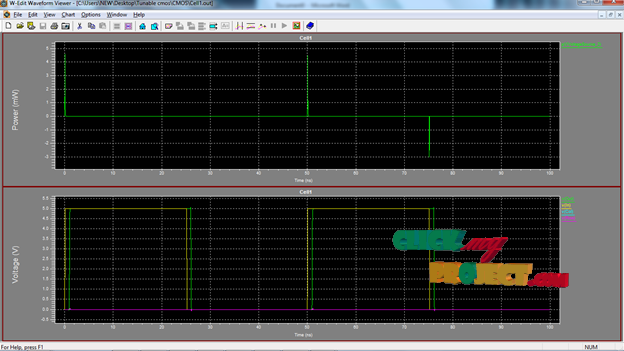

Nowadays the research works going on the pipelined ADC for power reduction and predictive error rate. The digital and analog circuit design have benefited from the speed, power, cost, and area improvements associated with technology time interleaved CDS. The Existing system reviews the pipeline ADC discusses the design challenges for switched-capacitor circuits in deep-submicron CMOS technology. In our proposed system has a novel CDS techniques using Time interleaved sampling design. The proposed work of the system is to analysis of the output noise range in the ADC. The main work of this system is improve the performance and also reduce the output power of the CDS design. The op-amp and comparator design mainly focus on the improvement of the system while ADC conversion of the system. a novel phase-dependent gain transition CDS technique, which is another efficient way to reduce prediction errors without using additional capacitors by utilizing a very low-gain op-amp. We reduce the prediction error by providing a slightly higher DC gain during the preamplifying phase, although this is still much lower than the gain of conventional op-amps commonly used in pipelined ADCs. To provide high gain, we apply the partially switched op-amp technique, in which auxiliary regulating amplifiers are turned on and are simply attached to the low-gain op-amps of the amplifying phase to form the folded cascade with the regulated gain-boosting amplifiers